# 6.004: Computation Structures

# Lecturers: Professor Daniel Sanchez and Dr. Silvina Hanono Wachman

Notes by: Andrew Lin

Fall 2020

# Introduction

This class is being taught virtually, so some improvements and changes to the class have been made over the summer.

Professor Sanchez and Dr. Wachman will be teaching the lectures (as returning lectures), and Professor Emer and Professor Han will be teaching recitations. But Professor Emer is the most senior of the staff – some of the ideas in this class were pioneered by him! There are also nine Teaching Assistants, who will be helping with labs, recitation sessions, and Piazza questions. But the most important component of this class is us – even though the class is very large, hopefully we'll all still be able to interact with the instructors and TAs. As a result, the lecture will be kept as close as possible to an in-person lecture: interactivity is encouraged.

In short, 6.004 is an introduction to the world of **digital systems**. Digital systems are actually quite new – the first computers, like the ENIAC in 1943, was installed in Philadelphia, weighed 30 tons, consumed 200 kilowatts (the lights dimmed when it was turned on), and it could only do about 1000 operations per second. Things have advanced in the last few decades dramatically: most laptops today weigh 1 kilogram, consume 10 watts, and can do about 10 billion operations per second.

# Fact 1

This kind of improvement is much faster than the rate for technology like cars, and computing devices are everywhere! Large and small systems are embedded everywhere in the world today, but even 15 years ago, many of these systems barely existed.

Our goal is to look at **how to physically implement computation**, with a bottom-up approach: we'll start with devices, materials, and atoms, building them up into combinational and sequential circuits, and then we'll use those to build a processor that can execute arbitrarily language in assembly. We'll think about how to make these fast, and then we'll move into computer systems (hardware and low-level software like virtual memory and operating systems) so that these systems we're constructing can be broadly useful.

These systems are very complex – each one has billions of devices, and they evolve very quickly. And the reason for this rapid evolution is that between each of these layers, there are **clean interfaces** of abstraction, like virtual machines and digital circuits. So this gives us a way to reason about the implementation without knowing the details:

# Example 2

The ENIAC and the laptop we're using today are both built using bits and logic gates, but these logic gates use completely different implementations.

This means that we'll have a **hierarchical design** built into this class: we'll make each level of the design simple to understand, and the class will be built on abstract "building blocks."

The first module of this class will be centered around **assembly language**: we'll understand how to go from highlevel programming languages, like those in 6.0001, to the basic language of computers. But then we'll go ahead and cover the topics of digital design, computer architecture, and computer systems.

The class will focus on **programmable general-purpose processors**, because microprocessors are the basic building block of computer systems – understanding them is important even if we're not planning on being hardware designers. Plus, they're the most sophisticated systems we have today – they have all of the tricks that make computations run efficiently, so they are a good vehicle for understanding design principles in hardware. Even if we think that "we will never design hardware in our own lives," it's important to note that more and more companies are designing specialized processors and accelerators today, so it's a great area to go into. And we'll see that designing hardware is actually similar in principle to designing software. By the end of the class, we'll be able to **design a simple processor from scratch**.

We'll do this by relying on modern design tools: **RISC-V** is a modern, open-source instruction set that's been gaining a lot of traction. And on the hardware side, hardware is going to be designed using **Minispec**, which is a hardware description language that was built specifically for 6.004. (It's basically a simplified version of the open-source **Bluespec**.)

This class will have two synchronous lectures per week – all slides, videos, and related materials will be posted on the website, https://6004.mit.edu. We'll also meet twice per week in recitations, which are designed to help us work through tutorial problems (which are similar to the quiz problems). Our assigned recitation sections are listed on the website, and we can let the instructors know via Piazza if we need to change sections.

#### Fact 3

Recitations will follow a **flipped model**, so students will work on tutorial problems together in small groups. In order for this to be successful, we should watch the previous lecture and attempt some post-lecture problems before each corresponding recitation.

Attendance at recitations is worth 5 percent of our grade, but we have four excused absences. Alternatively, we can opt out of recitation participation by October 2, in which case that percentage of the grade goes to quizzes instead. But the instructors encourage us to attend recitations, because they're an effective way for most students to learn the material.

In terms of assigned work, there will be seven mandatory lab exercises (with online submissions and virtual checkoffs to go over the labs) throughout the semester. To accommodate illnesses, unforeseen circumstances, and so on, there will be seven free late days. The class ends with an open-ended design project, and there are also three quizzes throughout the term (on October 1, November 10, and December 3, from 7:30-9:30).

Throughout the class, we're encouraged to ask questions by unmuting ourselves (if the question is specific to lecture) or by Zoom chat (if the questions are less direct but still related). And we should keep our video on if possible, because that helps us stay engaged and gives the professor nonverbal feedback. (Recordings won't include our video, and those recordings aren't publicly available anyway.)

About 50 percent of our total grade come from labs and the design project (80 and 20 points respectively), and the rest come from quizzes and participation (90 and 10 points). The fixed grade cutoffs will be at 165, 145, 125 points for an A, B, and C, respectively. An F grade is assigned if we receive less than 125 points or don't complete all of the labs.

The fastest way to get answers to questions will be the Piazza forum. Other than that, regular virtual office hours will be held to help us with any questions that we have – the schedule and lab queue are listed on the website.

# 1 September 1, 2020

The rest of this first lecture will dive into the first technical topic of this course, which is **binary number encoding and arithmetic**. The focus here is how computers store information and perform operations on numbers.

# Fact 4

Digital systems are called "digital," because they process information using discrete symbols called "digits." (This is in contrast to "analog" systems, which can have a continuous range of values.)

We often manipulate using the **binary digits** 0 or 1, though the implementation is often done by some analog system (for example, encoding 1 if some continuous voltage is above some value). In principle, we could use digits of any type, but the most common **encoding of numbers** is using binary or base 2, because certain operations like addition, comparisons, and logical operations (AND, OR) are very efficient when we only have two possible values per digit.

# **Definition 5**

A positive integer is encoded by assigning a weight (a power of 2) to each bit. Specifically, the value of a string of bits  $b_{N-1} \cdots b_0$  of length N is

$$v=\sum_{i=0}^{N-1}2^ib_i.$$

For example, the binary string 01111010000 encodes the number

$v = 0 \cdot 2^{11} + 1 \cdot 2^{10} + \dots = 1024 + 512 + 256 + 128 + 64 + 16 = 2000.$

Notice that the smallest number we can represent in an *N*-bit string is 0, and the largest number is  $2^N - 1$ . These correspond to the all-0s and all-1s strings, respectively.

Writing long strings of 0s and 1s often gets tedious, though, so these numbers are often **transcribed** into a **higherradix notation**. One popular choice is **hexadecimal**, where we use base  $2^4 = 16$  instead of base 2. To translate between hexadecimal and binary, we encode each group of 4 (binary) bits in a single hexadecimal digit: the digits are 0 through 9, followed by *A*, *B*, *C*, *D*, *E*, *F*. (For example, 1011 corresponds to *B*, and 0011 correspond to 3.)

#### Example 6

The binary string 011111010000 becomes the hexadecimal number 7*D*0. When we're mixing different bases, we often prepend the **base identifier**:

0b0111 1101 0000 = 0x7D0.

Here, the  ${\bf x}$  stands for "hex."

Addition and subtraction in base 2 look similar to that in base 10: for example,

$$1110_2 + 111_2 = 10101_2$$

,

keeping the "carries" into the next digit in mind. (This is the equation 14 + 7 = 21 in base 10.) Similarly, the equation 14 - 7 = 7 becomes

$$1110_2 - 111_2 = 111_2$$

,

where this time we need to remember to "borrow" accordingly from larger digits. But something more interesting happens if we try to do a subtraction like 3-5 = -2 in base 2: the issue is that we currently have no way to encode negative integers.

This issue is connected to another fundamental concept, which is that of **binary modular arithmetic**. If we force all of our strings to be of a fixed number of bits, addition or other operations might take our numbers outside of the allowed range of numbers! This is called an **overflow**, and often computers just ignore extra bits that go outside of the allowed range. In other words, we do all operations **modulo**  $2^N$ , meaning that numbers "wrap back around" every  $2^{N}$  in a clock-type structure. For example, if we constrain our subtraction 3-5=-2 to just three binary digits, we find that

$$011_2 - 101_2 \equiv 110_2 \mod 2^3$$

But we want to address the negative integer encoding more directly. One convention is to add an extra bit (the leftmost one), and let that one denote the sign. For example, we could say that

# $111111010000_2 = -2000$

(only the first digit has been changed to a 1 from the first example). But this is not actually a great idea: there are two different encodings for 0 (either 0 or -0). And then addition and subtraction will need to be more complex, which is why this representation is never used.

Instead, we're going to go back to the modular arithmetic idea: we want addition and subtraction to be operations around our "wheel modulo  $2^{N}$ ," so we'll relabel some of the digits. For example, instead of letting the strings (000, 001, 010, 011, 100, 101, 110, 111) represent the numbers 0 through 7, we can let them represent the numbers 0, 1, 2, 3, -4, -3, -2, -1 (in general, making exactly half of the numbers negative, so that the other half stay nonnegative). This is called the two's complement encoding, and what it basically means is that the most significant bit contributes a negative weight:

$$v = -2^{N-1}b_{N-1} + \sum_{i=0}^{N-2} 2^i b_i$$

This way, all of the negative numbers will still have a 1 in the highest-order bit, but this is still different from the sign-magnitude encoding. For example, the most negative number is encoded by the string  $10\cdots 0$ , which is  $-2^{N-1}$ , and the most positive number is encoded by the string  $01 \cdots 1$ , which is  $2^{N-1} - 1$ . (Meanwhile, the string of all bits now represents the number -1 – this is a good exercise to check, and it will come up frequently.)

Two's complement arithmetic is now much easier: for example, **negating a number** A can be done by inverting all bits (from 0 to 1 and vice versa), and then adding 1. We can check this with some arithmetic:

$$-A + A = 0 = -1 + 1$$

,

which means that

$$-A = (-1 - A) + 1.$$

But now the number -1-A is the binary number  $1 \cdots 1$ , minus the binary number  $A_{n-1} \cdots A_0$ . And now this subtraction has no "borrowing:" subtracting a digit  $A_i$  from 1 always flips the value, resulting in the **inverted** value  $\overline{A_i}$ . So -1 - Ais indeed the inverted number of A, and then we add 1 to get -A as above. And because A - B is the addition A + (-B), we can now use the same hardware circuit for addition and subtraction. For example,

$$3 - 6 = 0011_2 - 0110_2 = 0011_2 + 1010_2$$

(where the last step is turning 3 - 6 into 3 + (-6)), and then this addition gives us

$$= 1101_2 = -3.$$

In summary, our digital systems encode information using binary digits because this is the most efficient and reliable way to represent numbers. Using a two's complement encoding helps us keep arithmetic simple, and it allows us to represent both positive and negative numbers. And there are some post-lecture questions we should answer on the website before 10am tomorrow!

# 2 September 3, 2020

Today, we'll be introducing **assembly language and RISC-V**. (Before we begin, some logistics: the first lab for this class is being released today in a few hours, and lab hours will start tomorrow. Instructions on how to set up a GitHub repository are also listed on the website.)

### Fact 7

There will be an open Zoom room for lab hours, so we can feel like we are collaborating in a shared space.

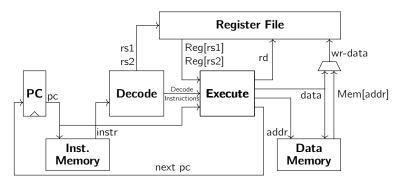

The point of today's lecture is to help us begin to understand how microprocessors actually work. As discussed last time, it would be great if our hardware could execute programs in Python or Java or other high-level languages, and our goal is to build such a **general-purpose** processor. But executing the features in such languages automatically is difficult, so we'll have our first level of abstraction today: **machine (or assembly) language**.

We can think of assembly language as an interface between hardware and software: we take our high-level languages, and we do some **software translation** (also known as **compiling**) to turn this into machine language that the microprocessor can understand. Those instructions can then be directly executed by our hardware.

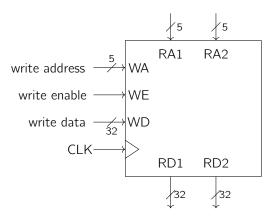

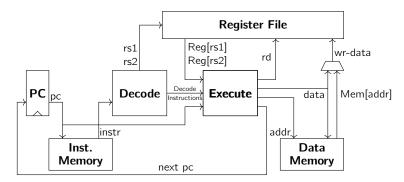

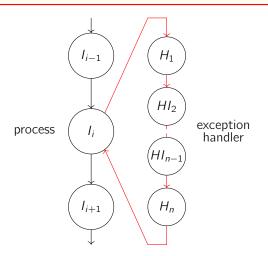

Every microprocessor has three main components:

- A register file is a grouping of registers, which are typically fixed size binary strings (about 32 bits). These register files are generally fast to access, and there are usually only a small number of registers (about 32).

- An **ALU**, or **arithmetic logic unit**, is where the main computations take place. This ALU works directly on the register file: it takes in sources from the register file, and outputs values to certain destinations in that register file.

- Main memory can be thought of as a very large (almost endless) storage which can handle all of our data storage needs. This holds both the contents of our program and the data needed during execution.

The reason for having both a register file and main memory is that we should store only a small amount of immediately needed data in our register file, so that it's easy to access and work with during computations. So we will also need a way to transfer information between those two components, and we need to design our machine language in a way that works well with these components.

# **Definition 8**

A **assembly language program** is a sequence of very basic operations which directly map to operations that our processor can perform.

There are basically three kinds of operations that such programs are allowed to perform:

- · ALU operations, which are certain primitive arithmetic operations,

- · Loads and stores, which are used to transfer information between the register file and memory, and

- Control transfer, which tells us to jump between locations (lines) in our program so we don't have to execute everything sequentially.

### Example 9

Let's start with a program and understand what our assembly language needs to express: consider the simple program sum =  $a[0] + a[1] + \cdots + a[n-1]$ .

Suppose that our array is larger than the register space we have, so it needs to live in our main memory. Then our array elements a[0], a[1], and so on, live at certain **addresses** in memory, and we also need to store other variables for the sake of computation: in this case, we'll label three variables as **base**, **n**, and **sum**, which tell us the starting address (in memory) of our array, the number of elements in the array, and the result of our computation.

Then our **register file** will need to store some selective information for our program to run: one way for this to work is if the first register stores the address of our current array element, the second one stores n, and the third stores our sum. Then our program might take the following steps:

- $x1 \leftarrow load(base)$ , which loads in the first address of our array,

- $x2 \leftarrow load(n)$ , which loads in the total number of elements to be adding up,

- $x3 \leftarrow 0$ , which initializes our sum to 0.

Now **loop** the following operations:

- $x4 \leftarrow load(Mem[x1])$ , which is a shorthand way of saying to get the element a[0] and put it into x4,

- add x3, x3, x4 (add to our rolling sum),

- addi x1, x1, 4 (increment the address we'll explain why we increment 4 later),

- addi x2, x2, -1 (decrement the number of remaining addends),

- bnez x2, loop (branch if x2 is not equal to zero, meaning that we return to loop).

store (sum)  $\leftarrow$  x3 (put the value back into our main memory to free up our register).

Here, "loads" and "stores" are the steps where we are accessing memory: **load** takes us from main memory into our register, and **store** takes us from our register into main memory.

We can compare the differences between a high level language and an assembly language:

- In a high level language, we can do complex arithmetic and use complex logical operations, while in an assembly language, we're limited to primitive versions of these.

- High level languages have arrays and dictionaries and similar data types and structures, but assembly only knows about bits and integers and similarly primitive data structures.

- We can use conditional statements and loops and so on in high level languages, but we can only use a few basic control transfer instructions in assembly.

- But high level languages cannot be directly implemented in hardware, while assembly language is designed to be implementable. Of course, it would be very tedious to program in assembly all the time, so we need a mechanism of doing this software translation.

#### Definition 10

An **instruction set architecture** (or **ISA**) specifies exactly what kind of storage we have available, the full list of processor operations allowed, and what format information needs to be sent in.

In 6.004, we'll use the RISC-V ISA, which is an open-source new architecture from Berkeley which is gaining a lot of traction. There are many variants – different data widths, certain extensions which support multiplication and division or floating point arithmetic – but we'll **stick to the basic RV32I** 32-bit integer processor in this class.

#### Fact 11

RISC stands for "reduced instruction set computer" – the concept is to support the minimum set of operations possible that can still accomplish the necessary goals. Ideally, this means we can build hardware that execute operations very quickly (we can avoid special cases and complicated instructions).

We'll now jump in to the full set of instructions for a RISC-V processor. In our specific case, everything is of size 32: the width of each register is 32 bits, and we'll call these 32-bit strings **words**. We also have 32 registers in our register file, labeled **x0** through **x31**. Out of these, **x0** is a special register which is hardwired to 0 - having a known value turns out to be very useful.

On the other hand, our main memory also stores in chunks of 32-bit words, but the number of locations is determined by the number of address bits that we have, and our **addresses will be 32 bits wide**. (In other words, the "location" of our memory is tracked by a binary string of length 32.)

**Remark 12.** For historical reasons, addresses are written and tracked in **bytes** (groups of 8 bits), meaning that 4 bytes form each word. So going from one 32-bit word to the next must increment us by 4 bytes, and that's why our addresses will often be  $0, 4, 8, \dots$ . Notice that because our addresses are stored as 32-bit strings, we can have  $\frac{1}{4} \cdot 2^{32} = 2^{30}$  words of main memory in our processor.

As mentioned above, the three types of operations are **computational** (or ALU), **loads and stores** (moving data), and **control flow** (telling the processor not to always go in order). We'll spend the rest of this lecure going through some specific operations.

**Computational instructions** come in four types, **arithmetic** (such as add and **sub**), **comparison** (slt, meaning "set less than," and **sltu**, meaning "set less than unsigned,"), **logical** (and, or, and xor), and **shift** (sl1 (shift left logical), **sr1** (shift right logical), and **sra** (shift right arithmetic)). We'll explain all of the computational instructions later on, but it's good to mention that "and" returns 1 if and only if both input bits are 1, "or" returns 0 if and only if both input bits are 1, and "xor" returns 1 if and only if the two input bits are the same. The important common thread between all of these is that the ALU **takes in two registers** as **source operands** and **outputs to one** as a **destination register**.

# Fact 13

If we want to perform an operation oper on src1 and src2, and we want to store that value in dest, then the syntax in our language is oper dest, src1, src2.

For example, add x3, x1, x2 tells us to put the contents of x1 and x2 together, and store the result in x3. Meanwhile, slt x3, x1, x2 tells us to compare x1 and x2: if x1 < x2, then we set x3 to 1, and otherwise we set x3 to 0. And sll x3, x1, x2 say to shift x1's contents left by the number of bits specified in x2, and then put the value in x3.

# Example 14

Suppose that our register currently has values x1 = 00101 and x2 = 00011. (Remember that the words of our register are supposed to be 32 bits wide, but we'll pretend they're 5 bits for now.)

If we want to run the operation add x3, x1, x2, then the binary integer 01000 will be stored in x3 (we can check the binary addition for ourselves). A more complicated example: if we want to run sll x3, x1, x2, we need to shift 00101 to the left by 00011 bits, and shift in zeros in the right. So 00101 becomes 01010, which then becomes 10100, which then becomes 01000 (note that we lose the leading 1 in this process). Then this string gets stored in our register location x3.

#### **Remark 15.** We always read before modifying, so something like add x1, x1, x2 doesn't cause any problems for us.

It turns out it's common to have one operand be from our register, but the other to come from a small constant encoded in the instruction itself (for example, incrementing a counter or adding 4 to the address). So even though we try to minimize the total number of operations, we still implement certain **register-immediate instructions**, which follow the format oper dest, src1, const (with const a constant replacing src2). For example, addi x3, x1, 3 uses the "add immediate" operation we store the value (x1 + 3) in the register location x3. And now we have the **full list of computational instructions** for the RISC-V processor: aside from the ones listed above, we also have addi (we don't need subi beacuse we can add a negative value), slti, sltiu, andi, ori, xori, slli, srli, and srai.

These instruction formats that we've described need to be written in a specific way so the processor can parse them, so there is a specific **register-register instruction format**. This instruction format comes in a 32-bit binary string, broken down as follows:

- Bits 0-6: Type of instruction format described. For example, 0110011 corresponds to this "reg-reg" format.

- Bits 7-11: Location of dest (the destination).

- Bits 15-19: Location of src1 (the first source).

- Bits 20-24: Location of src2.

- Bits 12-14 and 25-31: Encoding of the function itself.

On the other hand, a register-immediate instruction format (instruction format type 0010011 for "reg-imm") uses bits 7-11 to encode our destination, bits 12-14 to encode the function, bits 15-19 for the source 1 register, and bits 20-31 for our "const" or immediate value. Notice that this means our constant can only be up to 12 bits large (in two's complement binary, this means the number must fall in the range  $[-2^{11}, 2^{11} - 1]$ ).

#### Example 16

Suppose we wanted to execute the complex set of operations  $a = ((b+3) \gg c) - 1$ .

Even though all operations here are indeed logical operations that we've described already, we have to break this up into some basic computations, because each instruction can only specify two source operands and one destination. This is known as **three-address instruction**, and the breakdown looks something like

$$t0 = b + 3$$

,  $t1 = t0 \gg c$ ,  $a = t1 - 1$ .

If we wish to convert this to assembly, let's assume that a, b, c are stored in registers x1, x2, and x3, and we will store our temporary variables t0 and t1 in x4 and x5. Then the code becomes

# addi x4, x2, 3 srl x5, x4, x3 addi x1, x5, -1.

We'll now discuss some instructions that are slightly different from the basic logical operations described above. We'll briefly touch on lui first. Remember that our 32-bit instructions can't set all 32 bits of a register at once – in fact, even the register-immediate instructions can only deal with constants that are up to 12 bits long. So lui (load upper immediate) takes in an immediate value, appends 12 zeros to the end of it, and puts that value in the register. For example, something like lui x2, 0x3 would store the value 0x3000 (remember that in hexadecimal, each digit is four binary digits) in the spot x2. Basically, we often use lui to set the 20 upper bits of our register, while using the immediate instructions to set the other 12.

And the final type of instructions we'll discuss today are **control flow**, which is best illustrated with an example: if we want to run branching code like "if(a < b), then set c = a + 1. Else, set c = b + 2," we can use **conditional branch instructions**.

The format here looks like comp src1, src2, label, and this basically says to compare the values of src1 and src2. If the comparison returns "true," then we take the branch located at label label, and otherwise we continue executing our program.

Looking at what methods of comparison are allowed, RISC-V supports beq (branch equal), bne (branch not equal), and blt, bge, bltu, and bgeu (corresponding to  $<, \ge, <$  unsigned, and  $\ge$  unsigned). This concept of "signed versus unsigned" is that we typically consider binary strings to be two's complement numbers, but we can also treat them as positive binary numbers if we'd like. In summary, translating this code into assembly looks like the code below if we let x1, x2, x3 be the spots that *a*, *b*, *c* are stored:

bge x1, x2, else (this returns true if a < b is false),

addi x3, x1, 1 (in the case where a < b is true, increment by 1)

beq x0, x0, end (end the program for sure)

else: addi x3, x2, 2 (in the case where a < b is false, increment by 2).</pre>

Here, we're taking a branch when we have  $a \ge b$ , in which case we go straight to our **else** statement. The third line always returns true, so we'll always take that branch to skip the "else" line – we should be careful when working with assembly language to watch out for this kind of thing!

We'll continue next time with unconditional branches, loads, and stores.

# 3 September 8, 2020

Our first lab will be due next Thursday, and checkoffs for it start this Friday (we can find the signup form on Piazza). As a reminder, there is a Zoom room that we can join to emulate the "6.004 lab room" while we're waiting on the queue to get help.

The main topic of this lecture is **compiling code and implementing procedures** in RISC-V assembly, but we'll start by explaining a few more commands that weren't covered last class.

Recall that RISC-V has three kinds of allowed instructions:

- 1. Computational instructions executed by the ALU (which are either **register-register**, taking the form oper dest, src1, scr2, or **register-immediate**, taking the form oper dest, src1, const),

- Control flow instructions (which are either conditional branch instructions of the form branch-comparison src1, src2, label, telling us whether or not to jump to the location with a certain label, or unconditional branch instructions, which we'll explore today), and

- 3. Loads and stores of the form lw dest, offset(base) or sw dest, offset(base), which help us read and write information between main memory and our register.

We'll also clarify the purpose and usage of **pseudoinstructions**, which are shorthand notation for other instructions or sets of instructions.

# Fact 17

Recall that one way we can achieve an "unconditional branch" to skip over certain lines of code (for instance, to skip past a few lines of code in control flow) is to run a command like beq x0, x0, end.

Since x0 = x0 is always true, this will always jump to the location labeled with end. But RISC-V also has explicit unconditional branching, and we'll see soon why this is necessary.

# **Definition 18**

The operation jal serves as an unconditional jump and link.

For example, the code jal x3, label will jump to the label (encoded as an offset from our current instruction), and then the link (which we'll discuss later in the lecture) will be stored in x3. Note that in the actual 32-bit string that encodes this instruction, there are **20 bits** where we can encode an immediate.

We can also use the operation jalr, which is an **unconditional jump via register and link**. This can be written for instance as jalr x3, 4(x1): this jumps to the address which is four after the memory address stored in x1. With these two commands together, we'll be able to jump to any 32-bit address we want.

So now we can talk about how to access memory values and do computations on that memory. There isn't an instruction that can take two addresses in memory, add the values of those two words together, and put the sum in a different, so something like a = b + c doesn't work as a single instruction in RISC-V. Instead, we need to run the following pseudocode on the left:

| $x1 \leftarrow load(Mem[0x4])$    | lw x1, 0x4(x0)                     |

|-----------------------------------|------------------------------------|

| x12 load(Mem[0x8])                | lw x1, 0x4(x0)<br>lw x2, 0x8(x0)   |

| $x3 \leftarrow x1 + x2$           | add x3, x1, x2<br>sw x3, 0x10(x0). |

| store(Mem[0x10]) $\leftarrow$ x3. | sw x3, 0x10(x0).                   |

But memory addresses are specified in RISC-V as a pair (base address, offset). The base address needs to be stored in a register, and the offset is some 12 bit constant that we include in the instruction. In assembly, this ends up looking like the code on the right: because we're taking all addresses as offsets from 0, we're using x0, hard-coded to 0, as the base address.

# Example 19

Now we're ready to take another look at how to implement our program for summing array elements. Recall the setup: our array is stored in consecutive addresses of our main memory, and we also have three variables **base** (the location of our array's start), **n** (the number of array elements), and **sum** (the place where the sum should end up going in main memory)

For reference, the half-pseudocode from last week is shown on the left. We assume that x10 already contains the address of base, which is (in turn) the starting address of our array in main memory.

| x1 $\leftarrow$ load(base)    | lw x1, 0x0(x10)                                                                                 |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------|--|--|

| $x2 \leftarrow load(n)$       | lw x1, 0x0(x10)<br>lw x2, 0x4(x10)<br>add x3, x0, x0                                            |  |  |

| $x3 \leftarrow 0$             | add x3, x0, x0                                                                                  |  |  |

|                               |                                                                                                 |  |  |

| loop:                         | loop:                                                                                           |  |  |

| $x4 \leftarrow load(Mem[x1])$ | loop:<br>lw x4, 0x0(x1)<br>add x3, x3, x4<br>addi x1, x1, 4<br>addi x2, x2, -1<br>bnez x2, loop |  |  |

| add x3, x3, x4                | add x3, x3, x4                                                                                  |  |  |

| addi x1, x1, 4                | addi x1, x1, 4                                                                                  |  |  |

| addi x2, x2, -1               | addi x2, x2, -1                                                                                 |  |  |

| bnez x2, loop                 | bnez x2, loop                                                                                   |  |  |

|                               |                                                                                                 |  |  |

| store(sum) $\leftarrow$ x3.   | sw x3, 0x8(x10).                                                                                |  |  |

All that's really left to do is to convert the beginning and end of the program to "loads" and "stores," and we've done that on the right. The most important thing to note is that loads and stores always look at addresses relative to some register value (in this case, either x1 or x10).

The final set of "instructions" we'll consider are **pseudoinstructions**, which aren't actual RISC-V instructions but serve as aliases to them for easier coding.

# Example 20

The command  $mv x_2$ , x1 (here mv stands for "move") is equivalent to addi x2, x1, 0 – both of these mean that we copy the value of x1 to x2. Meanwhile, ble x1, x2, label is equivalent to bge x2, x1, label.

#### Example 21

For a more complicated example, li x2,3 (standing for "load immediate") will translate directly into addi x2, x0, 3 since the constant is small enough, but we can also load larger numbers like li x3, 0x4321: this will be split into the two instructions lui x3, 0x4 and addi x3, x3, 0x321, because addi is only able to encode up to 12-bit constants.

**Remark 22.** There's another component of the machine here, called an **assembler**, which translates these instructions into binary and does the hard work of putting everything into 32-bit binary strings. (For example, it can tell which of the two use cases of **1i** to assemble.) But we won't look at that too much here.

# Example 23

Suppose our machine is in a state where the values 0x35, 0x3, 0x9, 0x1, 0x22, 0x23, 0x21, 0x16, 0x18 are stored in the first addresses 0x0, 0x4, 0x8, 0xC, 0x10, 0x14, 0x18, 0x1C, and 0x20, respectively. Also, suppose our register file has initialized the values of 0x8 and 0x14 in x2 and x3.

We'll try performing a series of instructions:

- The instruction add x1, x2, x3 will put the value 0x1C in x1, and mv x4, x3 will put 0x14 in x4.

- If we run the instruction 1w x5, 0(x3), we'll fetch the value at main memory with address 0x14 (which is the value in x3), and therefore register x5 will have value 0x23.

- Similarly, the instruction lw x6, 8(x3) will skip two words past 0x14, so we'll write 0x16 into x6.

- And the operation sw x6, 0xC(x3) will put the value 0x16 (which is currently in x6) into the address 0xC + 0x14 = 0x20.

For the rest of this class, we'll talk about **compiling simple expressions into RISC-V code** and some relevant complications that come up. In other words, if we have some C or Python code, how can we turn it into assembly? Here are some concepts to keep in mind:

- Assign variables to registers that is, decide which variables and temporary variables correspond to which registers.

- Translate operators into computational instructions (like add or or),

- Use register-immediate instructions (like addi) when we're dealing with operations with small constants and li for larger constants.

For example, if we want to run the two commands y = (x+3) | (y + 123456) and  $z = (x * 4) ^ y$ , we'll need to break down the complex instructions into simpler ones. First, we'll assign x, y, z to the registers x10, x11, and x12, and we'll use x13 and x14 for temporary variables. Then the code looks as follows:

```

addi x13, x10, 3 (to create (x + 3))

li x14, 123456

add x14, x11, x14 (to create y + 123456)

or x11, x13, x14 (to finish evaluating y)

slli x13, x10, 2 (to multiply x by 4)

```

xor x12, x13, x11 (complete the final operation).

Conditional statements are a bit more difficult, but we can do those systematically as well. For example, an **if statement** of the form "if (expression), then execute (if-body)" can be written schematically as

compile (expression) into a register xN beqz xN, endif compile (if-body) here endif:

#### Example 24

Suppose we have two integers x, y, and we want to execute the instruction "y = y - x" if x < y.

We can put the variable x in x10 and y in x11. Then following the schematic above, our RISC-V code is

```

slt x12, x10, x11

beqz x12, endif

sub x11, x11, x10

endif:

```

Of course, we can actually combine the "expression" and the "branch" at times: in this case, the first two operations can be combined into the single command bge x10, x11, endif, because we're doing an ordinary comparison.

**If-else statements** work similarly, but are a little bit more complicated. The schematic for "if (expression), then execute (if-body), otherwise execute (else-body)" is below:

```

compile (expression) into a register xN

beqz xN, else

compile (if-body) here

j endif (that is, jump straight to endif)

else:

compile (else-body) here

endif.

```

And **while loops** are also similar: if we want to execute a statement "do (while-body) while (expression) is true," then we can run this list of commands:

compile (expression) into a register xN beqz xN, endwhile compile (while-body) here j while endwhile.

But we can have less branch/jump instructions by putting the comparison at the end instead, as below:

j compare (ensuring that we still check the (expression) condition first)

loop:

compile (while-body) here

compare:

compile (expression) into a register xN

bnez xN, loop.

This is nice because there is only one control-flow instruction, which is the bnez one at the end.

And what we've learned is enough to implement the **Euclidean algorithm** to find the GCD of two positive integers (which subtracts the smaller of the two numbers from the larger until they are equal). Such a sequence of code can be executed with many different initial values, so it's valuable to try to "call" this snippet multiple times:

# **Definition 25**

A **procedure** or **function** or **subroutine** is a reusable code fragment which performs some specific task. Such a procedure has a named entry point (the name of the function), some number of formal arguments (possibly zero), and local storage, and it returns to the caller when it completes.

Such a **caller** must be able to pass arguments to our procedure and get values back when the procedure finishes, and the convention is to **use registers for both of these purposes**. To make sure procedures are implemented correctly, there are a specific set of rules specified by a **calling convention**, so that all developers can safely call procedures without breaking code.

The RISC-V calling convention gives the registers symbolic names:

#### Example 26

For example, the registers x10 through x17 have the symbolic names a0 through a7, and they're known as "argument registers." We use the first two of these, x10 and x11 for returning values from our function.

To illustrate this idea of "calling" a little more, suppose that we've written a code fragment that sums up the elements of an array, given the necessary variables above. If we wanted to execute this code fragment in a larger program, we could put a label that led us straight to the "sum" fragment, but the problem is that **we need to know** how to go back to whatever location we were at in our main code, even if we call the sum function multiple times.

So we need to remember our return address (that is, when our procedure was called from), and that's done through the **RA** (return address) register. Every time a procedure is called, our current address is stored, and we do a **procedure call** by using the command **jal ra**, **label**. This puts the address (4+the procedure call address) in our register **ra**, so that the procedure will return to the correct next command by running **jr ra** at conclusion. (By convention, **x1** is often used for storing this return address.)

One issue, though, is that we shouldn't have to worry about saving registers for **nested procedures**: each procedure should be able to use all registers, regardless of how any of its procedures are acting! So when a procedure is running, the values of the relevant registers must be stored and restored at the end of the procedure; it is the **callee**'s responsibility to save registers in spots x8-9, x18-27 (these have the symbolic name s0 through s11). In contrast, the caller has some registers that it needs to save as well (such as x1, the return address, and x10 through x17, the function arguments). So any procedure call needs to have a local storage component, known as an **activation record**, which

stores (in a **stack** in main memory) any memory allocations that don't fit in the registers. Basically, the most current procedure is always at the top of the stack, and it is deallocated when the procedure exits.

This distinction between caller-saved and callee-saved registers is important to keep in mind – the former is not preserved across function calls, but the latter is, so certain arguments must be saved on the stack to preserve values. We'll discuss this more later on in the class.

# 4 September 10, 2020

We'll conclude our discussion of assembly language today, looking closer at procedures, stacks, and MMIO.

As a reminder, we discussed the **three components of a microprocessor** in an earlier lecture: basically, we have a register file (to store certain information), a main memory (which holds our program and data), and an arithmetic logic unit. But there's one more special register, which we'll discuss now.

#### Definition 27

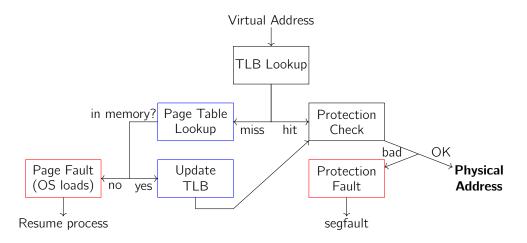

The **program counter** is a special register (not part of the main set of 32) which keeps track of the address of our current instruction.

If we're running loads or stores or computation, the program counter is always incremented by 4 (bytes) to get to the next instruction word in memory. But there are some special cases – if we have a control flow instruction, for example, we may need to update the program counter differently.

#### Example 28

Suppose we have an instruction blt x1, x2, label. Then the program counter needs to jump to some address if x1 < x2, and otherwise it gets incremented by 4 (as usual).

Remember that all instructions, including these branch instructions, are stored as 32-bit binary values in memory. So we want to understand how these instructions actually look, and that requires a more schematic understanding of our main memory.

We'll look at the RISC-V calling convention more carefully for this. Remember that we have various symbolic names for our registers: for example, the a0 through a7 registers are used for function arguments (out of which a0 and sometimes a1 are used for return values), and the ra register stores the address that we need to return to after completing a procedure. Other than this, we have the t0 through t6 temporary registers, the s0 through s11 saved registers, as well as the stack point sp, global pointer gp, thread pointer tp, and zero register zero.

# **Definition 29**

A **caller-saved register** is one that is not preserved across function calls, meaning it must be saved by the caller before a procedure if its value needs to be preserved. Meanwhile, a **callee-saved register** is one that must be preserved, meaning it must be saved by the callee and restored before completing the procedure and returning control.

Examples of caller-saved registers include the argument, temporary, and return address registers, and examples of callee-saved registers include the saved and stack pointer registers.

We also discussed the necessity of **storing certain information** that our code may need to use later, such as local variables, registers that need to be saved, and data that doesn't fit in our 32 registers. The idea is that we allocate

space for **activation records** of each procedure: if procedure *A* needs to call procedure *B*, then the activation record for procedure *B* gets put in memory "above" procedure *A*'s, and once procedure *B* is done, its record is deallocated. This **stack** (last-in-first-out) structure means that **whatever is at the top of our stack is going to be our current procedure**, and therefore keeping track of memory allocation is easiest.

This RISC-V stack is stored in a specific spot in memory: we have the stack grow from **higher to lower addresses**, and we make sure the stack pointer **sp** always points to the top of the stack. So if we want to add a register's, say **a1**'s, value to the top of the stack, we can run the following "push sequence" commands:

```

addi sp, sp, -4

a1, 0(sp).

```

Then when we want to restore a value or complete a procedure, we can run the following "pop sequence" commands:

lw a1, O(sp) addi sp, sp, 4.

The key point is that **the memory is always available to us, but we need to return it the way that we found it**. So a procedure can add an arbitrarily large activation record, but it must take everything off the stack at the end.

#### Example 30

The sequence of commands (at the beginning of the procedure) addi sp, sp, -8, sw ra, O(sp), sw a1, 4(sp) can be reversed with the exit sequence (at the end of the procedure) lw ra, O(sp), lw a1, 4(sp), addi sp, sp, 8, jr ra.

#### **Example 31** (Callee-saved registers)

Suppose we want to implement the function f(x, y) = (x+3)|(y+123456) by storing intermediate values in the s0 and s1 registers.

Then our function will run the following arithmetic commands:

addi s0, a0, 3 li s1, 123456 add s1, a1, s1 or a0, s0, s1.

However, before we do any of this, we need to make sure to **save the values of the s registers**, because they're callee-saved registers! So at the beginning of our function, we should allocate two words of space on the stack and store the **s** registers by running the command addi sp, sp, -8, followed by sw s0, 0(sp), and sw s1, 4(sp). Then at the end, we reverse with the exit sequence lw s0, 0(sp), lw s1, 4(sp), addi sp, sp, 8, and finally jr ra, so that we exit with the stack status as we first saw it.

**Remark 32.** At the end of this process, the values of saved s0 and s1 still exist in memory, but the stack pointer is moved back to a higher address, so it's effectively like we've cleared those words from memory.

# Example 33 (Caller-saved registers)

Suppose that a caller is storing the values 1,2 for x, y, and then we want to call a function sum to find z = sum(x, y) and finally store w = sum(z, y).

There are a few relevant concepts here. First of all, because we want to call another procedure, namely **sum**, we want to make sure to save the relevant registers that might be overridden. So instead of directly running the below code:

# li a0, 1 a1, 2 jal ra, sum,

we want to save the registers ra and a1. Here, the former needs to be saved so that we can jump back from the sum subroutine properly, and the latter needs to be saved by convention because we are reusing the value of y a second time later in the code. (We don't need to save a0, because we never need the value of x again.) That means that we need to run the commands addi sp, sp, -8, sw ra, 0(sp), and sw a1, 4(sp).

**Remark 34.** An important principle is that callers don't see the implementations of the callee's procedures. So even if it seems like the most natural way to implement **sum** is just to run add a0, a0, a1, which doesn't modify a1, convention still tells us that we should save a1 if we need it later.

After running that jal ra, sum command above, we have the value of z in a0, and we need to restore the value of y again via lw a1, r(sp). Then we can call jal ra, sum again, and that gets the value of w in register a0, as desired. We can then finish by just running lw ra, 0(sp) and addi sp, sp, 8 to return the stack and stack pointer to their original state.

In summary, callers are responsible for saving a, t, and ra registers, while callees are responsible for saving s registers. But both need to make sure the stack pointer is in the right spot at the end of the procedure.

#### Fact 35

Two relevant pseudoinstructions are **call func** (for the caller to jump-and-link) and **ret** (for the callee to return from the subroutine).

In the remaining time, we'll discuss some more complicated cases, such as the case of **nested procedure**. The return address **ra** is always supposed to be caller-saved, so we just need to be careful to store and load the value of **ra** before and after calling any procedures. **As long as each procedure maintains and properly restores the relevant data**, the convention will hold up in this case.

For another complex situation, we can also consider data structures that are too large to store in our registers. For example, if we want to find the maximum value in a large array, we can just keep track of the two variables **(base address)** and **(size)**, rather than passing the whole array in. Our "maximum" subroutine would then do the following:

- Start off with the base address and the size of the array as the values of a0, a1.

- Initialize some local variables t0, t1 to zero, corresponding to "i," our current array index, and "max," our rolling maximum.

- In our loop, check whether  $t_0 < a_1$  (meaning that we still have something in the array to compare against).

- Load the word from the location  $a0 + 4 \cdot t0$  (which is the address of the ith element of our array).

- Compare the loaded word to our maximum value stored in t1, and move the value if necessary.

- Increment the index t0 by one and check our loop condition again.

This finishes our discussion of the RISC-V instruction architecture, and now we have the necessary language to be able to translate any high-level program into RISC-V! It's just good for us to keep in mind that whenever we have data structures like dictionaries, they're always going to be implemented with blocks of memory with words that refer to various addresses.

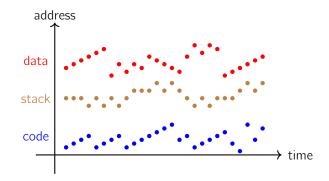

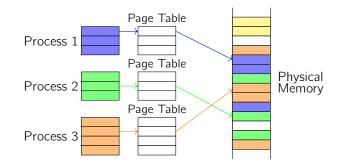

We'll finish by understanding how this all fits together into the memory layout that we're using. Most languages actually use **several distinct memory regions** for data:

- Stack (for procedure calls),

- Static (for global variables that exist throughout the program),

- Heap (for dynamically-allocated data). In languages like C, this heap needs to be manually managed with the commands malloc() and free(), but in languages like Python or Java, the system will automatically make new space when we declare an object like a dictionary.

- The text of our code.

In RISC-V, we put the **text, static, and heap regions** in memory consecutively, starting from the smallest address 0x0. (In other words, the heap grows towards higher addresses as we allocate more memory for it.) This is why, in contrast, the stack starts from the highest address 0xFF. F and grows towards lower addresses – we can allow flexible space for both the heap and the stack.

Finally, we have some specific pointers: the **stack pointer** sp points to the top of our stack, the **global pointer** gp points to the beginning of our static region (which we won't use in 6.004), and the **program counter** pc looks at the line of code that we're currently executing.

In our next lab, we'll also get to think about how this all relates to **inputs and outputs**. Recall that our high-level programs are translated using RISC-V (or other ISA) into instructions that our processor knows how to use. But there are other pieces of hardware that we may interact with, such as a display (to print to) or a keyboard (to get inputs from), or other peripherals. So **special dedicated addresses** are used to represent these input/output (I/O) devices: we can then just use **1**w or **s**w instructions to read or write accordingly. This is known as **memory mapped IO** (or **MMIO** for short), and this means that we can only use those specific addresses for input/output, not regular storage. And there are special I/O devices that respond to memory requests, rather than main memory.

# Fact 36

Each time we perform a 1w instruction from the address 0x4000 4000, we will read one signed word from a keyboard. Meanwhile, if we perform a sw instruction to 0x4000 0000, we print an ASCII character, and if we perform a sw instruction to 0x4000 0008, respectively, we print a decimal or hexadecimal number.

#### Example 37

Here is an example of a program that reads in two inputs from our keyboard, adds them together, and then displays the result on an output monitor.

As always, we need to remember that loads and stores must be done with addresses relative to the value stored in some register.

```

li t0, 0x40004000 (loads the address of the "read port")

lw a0, 0(t0) (reads in the first input word)

lw a1, 0(t0) (reads in the second word)

add a0, a0, a1

li t0, 0x40000004 (loads the address of the "write port")

sw a0, 0(t0).

```

And we can use MMIO for certain **performance measures** as well: we can get the **instruction count** (loading from 0x4000 5000) to learn how many instructions have been executed since the program started, or get the **performance counter** (loading from 0x4000 6000) to count the number of instructions since we have turned the counter on (which is toggled off/on by storing 0 or 1 in 0x4000 6004). So this is a way for us to track how long a piece of code takes to run!

With all of this knowledge about assembly language, we now understand what we need to build, and we're going to try to understand how to build the hardware to implement those assembly instructions (from the bottom up) in the next few lectures.

# 5 September 15, 2020

Today, we're going to switch gears and turn away from assembly language (which was the first module of our course). We'll start discussing **digital design** now, looking at combinational and sequential circuits, and understanding why the ISA structures are set up in the way they are. Specifically, one goal is to understand (from the hardware point of view) what constraints exist in design and what makes our systems most efficient.

To reiterate a point from earlier on in the class, even if we don't build hardware in our professional lives in the future, we'll probably still be designing some cutting-edge systems, so we'll need good knowledge of hardware. More importantly, in the modern world, systems are becoming more specialized. Performance improvements from general-purpose processors are reaching their limits – if we look at the performance of processors since the 80s, we've had a dramatic (50000-fold) improvement, mostly first following Moore's law (telling us we can have an exponential number of transistors on the chip) and then following Dennard scaling. But in the present, those kinds of performance improvements have basically stopped, and companies are now starting to build custom hardware to meet their needs. So we will likely need to **use and design specialized hardware**, rather than just sticking to general-purpose processors.

Thus, the first topic of this module is **digital abstraction** – building digital conventions for storing and processing information.

#### **Definition 38**

**Analog** systems represent and process information by keeping track of continuous signals, while **digital** systems do so by recording in discrete symbols.

This means that an analog system keeping track of voltage, or current, or temperature, or pressure, can record down the exact value of any of these quantities and use that information in its processing and its circuits. But a digital system encodes this kind of information by keeping track only of **ranges of physical quantities**, and we often do this in binary (recording down a "0" or "1").

So, for instance, if our digital device measures the voltage V through some component of a circuit to be larger than some value, we encode that as a 1, and if we measure it to be below that value, it is a 0. But the key advantage to keep in mind for these digital systems is that **they should tolerate noise**.

# Example 39

Consider an **analog audio equalizer**, which takes in some voltage signal which represents sound pressure (in decibels) over time. This signal goes into our system, and we use the audio equalizer to adjust the amplitude of various frequencies of the signal.

(For example, maybe we want to increase our bass or our treble sound in a music track.) The way this works in practice is that we have some **band filters** to get low, middle, or high frequencies that filter different components of our sound. Then we amplify each of those components with some gain. Finally, we mix these together and get some output.

But in reality, there are going to be some differences between the output that we have and what we expect. There are many reasons why such a system may not work: various sources of noise will make their way into the system, manufacturing variations for resistors or capacitors may change the gain, and degradation of the different components also alters the sound over the time. So this is not a good way to build reliable systems, because we want to be able to process the same information over and over again, without having the output dominated by noise.

#### Fact 40

By switching to digital systems, we're making an abstraction that allows us to tolerate some amount of noise. So even though we want our bits (0 and 1) to behave perfectly, there is still going to be some real-world noise, and we're just trying to engineer the world to behave in a digital way.

So let's think about how we can take a continuous quantity like **voltage** and turn it into a discrete (digital) quantity (like **0** or **1**). Whatever convention we use should be uniformly adapted across all circuit components in our hardware.

# Example 41

Let's try defining a threshold voltage  $V_T$ , and we can say that every component and wire in our system interprets  $V < V_T$  as a "0" and  $V \ge V_T$  as a "1."

This isn't a great system, because a slight amount of noise can flip a 0 to a 1 or vice versa, if the voltage is right at the edge of  $V_T$ . So we'll add some elbow room:

#### Example 42

Now, let's try having two thresholds  $V_L < V_H$  (low and high). If the voltage satisfies  $V \le V_L$ , we interpret that as a 0, and if the voltage is  $V \ge V_H$ , we interpret that as a 1. If we're in between the two values, we say that the bit is undefined.

Building a device that distinguishes between these voltages is not hard to do, but this isn't a great system either, because of one specific problem: **differences between inputs and outputs**. There are still going to be values right around the valid-invalid regions! If we have an input device which sends a valid 0, but it's transmitting a signal at voltage  $V_L - \varepsilon$ , it's possible that noise will turn it into  $V_L + \varepsilon$  by the time it hits another (output) device in the circuit. So the 0 still turns into an undefined bit, and we run into issues with degradation again.

To address this, we make a distinction between input and output bits:

# Fact 43

Any convention for our digital systems should use **narrower ranges for output voltages than input voltages**, so signals will still be valid with noise.

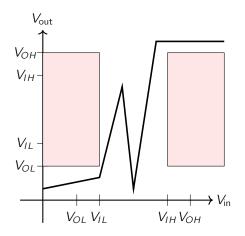

We'll use four different thresholds now, which we denote  $V_{OL}$ ,  $V_{OH}$  (for "output low" and "output high") and  $V_{IL}$ ,  $V_{IH}$  (for "input low" and "input high"). But now, a digital output device outputs a 0 if the voltage V is below  $V_{OL}$  and a 1 if it's above  $V_{OH}$ , and similarly a digital input device reads a 0 if the voltage is below  $V_{IL}$  and a 1 is above  $V_{IH}$ . To avoid the previous problem, we need to make sure that

$$V_{OL} < V_{IL} < V_{IH} < V_{OH}.$$

In words, digital devices are supposed to accept "marginal inputs" and "unquestionable outputs," so that an output of a 0 or 1 from some device won't turn into an undefined or opposite bit when it is read into another input device.

# Fact 44

The key point is that digital systems are **restorative**: noise does not accumulate like it does in analog systems.

For example, if we have a digital circuit which takes in some voltage V and then applies some functions f and g, we might get composite noise that looks like

$$g(f(V+\varepsilon_1)+\varepsilon_2)$$

by the time we're done running through. But in a digital system,  $f(V + \varepsilon_1)$  and f(V) are the same as long as our thresholds are properly calibrated, and similarly  $g(f(V) + \varepsilon_2)$  and g(f(V)) will be the same, too. So **the noise will be canceled at each stage**, and this is important so that (for example) index counters won't randomly decrease by 1 because of accumulated noise.

**Remark 45.** Note that any noise cancellation (that is, any system that is "fighting noise") requires **active components**, which are feeding energy into the system from an external source.

We can formalize this whole idea further by analyzing simple digital devices. Let's consider a **buffer**, which copies the input value into the output (so feeding in a 0 gives us a 0, and feeding in a 1 gives us a 1).

### Definition 46

A voltage transfer characteristic (VTC) plots the output voltage as a function of the input voltage.

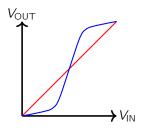

We find this by inputting in various values of  $V_{in}$  and then waiting for transient behavior to go away, and recording the subsequent value as  $V_{out}$ . Here's an example of a VTC:

Even though the buffer is just supposed to copy over the input value, it's not good enough to just copy the voltage from  $V_{in}$  to  $V_{out}$  because of noise. And note that our VTC needs to avoid the **forbidden zones** which are shaded above: those are the regions where we feed in a valid input, but we end up with an invalid output.

Because  $V_{OH}$  and  $V_{OL}$  have a difference larger than  $V_{IL}$  and  $V_{IH}$ , our VTC needs to "rise very quickly" in the middle of the diagram: the value of  $\left|\frac{dV_{out}}{dV_m}\right|$ , also called the **gain**, must be larger than 1 at some point in the middle, so that means **we need to have an active device** which feeds in energy (even though, again, we're just copying a bit!). But also, this VTC can do anything in the range of inputs between  $V_{IL}$  and  $V_{IH}$ : it's perfectly fine to have valid digital outputs for invalid digital inputs, for example. (Really, all that matters here is that whenever our input voltage is less than  $V_{IL}$  or larger than  $V_{IH}$ , we get the right answer.)

So we can start looking at **digital circuits** now, and in the next 7 lectures or so, we'll study different types of digital circuits. There are basically two kinds:

- **Combinational** circuits do not have memory, so each output of the circuit is only a function of the input values. For example, the **buffer** and **inverter** each take in a bit, and they output a bit based on the input. We can also have gates like **AND**, which take in multiple inputs.

- **Sequential** circuits have some internal memory or state, so the output of the device depends on both the internal state and on the inputs that are fed in.

We'll start looking at combinational circuits right now and continue this over the next few lectures.

#### **Definition 47**

A **combinational device** is a circuit element with digital inputs and outputs (working according to the above specification), as well as:

- A functional specification which exhaustively specifies output behavior for all possible input values, and

- A timing specification, which tells us (at least) how much time we need before the output has a valid digital value. This time *t*<sub>PD</sub> is called the **propagation delay**.

For example, a combinational device's specification can consist of the following information: "The device will output a 1 if at least 2 of the 3 inputs are 1s, and otherwise it will output 0. A valid output will be generated within 2 nanoseconds." The above components and rules in the definition are called the **static discipline**, and the reason we need them is that combinational devices can be put together and connected in large, predictable circuits.

#### **Definition 48**

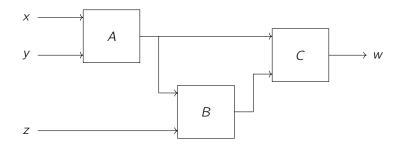

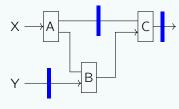

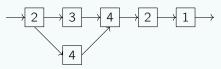

A set of connected elements is called a **combinational device** if:

- · each circuit element is a combinational device,

- · each input is connected either to one output or to a fixed constant 0 or 1, and

- there are no directed cycles in the circuit.

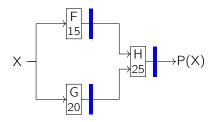

Here is an example:

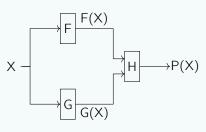

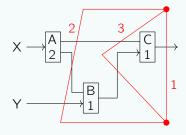

This device is indeed a combinational device as long as A, B, C are combinational devices, because we have digital inputs and outputs, and we can derive a functional description by writing out the function f in terms of the functions of the devices  $f_A$ ,  $f_B$ ,  $f_C$ : it will be

$$f(x, y, z) = f_C(f_A(x, y), f_B(f_A(x, y), z)).$$

The point is that we do indeed have a functional specification, and now we can find the propagation delay by thinking about the longest path through the circuit: in this case it's the one that goes through all three combinational devices, and we have

$$t_{PD} = t_{PD,A} + t_{PD,B} + t_{PD,C}.$$

Let's think about what goes wrong if we violate any of the conditions for a set of circuit elements being a combinational device. It's important that every input is connected to exactly one output – otherwise, our combinational device may stop working if some input isn't connected properly to the rest of the system, or we might overwrite important data or have different outputs conflicting with each other. (But this is a sufficient condition, not a necessary one – sometimes it's okay for us to have combinational circuits that run in parallel, as long as we don't get conflicting data.) And it's pretty easy to come up with examples where having cycles in our combinational circuits is bad: for example, if an output feeds back into an earlier combinational device, we may get oscillating behavior.

We'll start talking about functional specifications next lecture, but the main point is that we can specify functions in various ways. There are two main systematic approaches we'll take: we can use **truth tables**, where we enumerate outputs for all possible inputs, and **Boolean expressions**, which use AND, OR, and NOT operations. (We'll discuss / review Boolean algebra next time.) The point is that **any combinational circuit can be expressed with Boolean expressions** and **truth tables**, and the former is easier to optimize.

In summary, digital systems tolerate noise much better than analog systems, and we can encode voltages by using certain margins and voltage levels. Next time, we'll start studying combinational devices in more depth.

# 6 September 17, 2020

We'll continue our journey into digital design today, looking at **Boolean algebra and logic synthesis**. Last time, we came up with a digital signaling **discipline** that was robust against noise and helped interface different input and

output devices together, and today we'll get into the functional aspect of combinational circuits.

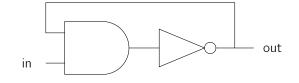

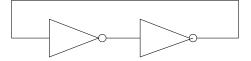

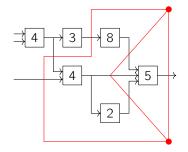

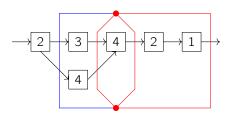

Recall that combinational devices are circuits with a **static discipline** containing digital inputs and outputs, a functional specification, and a timing specification (which contains at least the propagation delay for the device). We then composed such devices together, with the rules that all components must be combinational, all inputs must be connected to one output or a constant, and there must not be directed cycles. Feedback loops like the one below explain why certain circuits can't always reach a known or stable value if they contain directed cycles:

This circuit contains an AND gate and an inverter (we can tell the difference between an inverter and a buffer by the circle at the tip). The point is that if our input bit is 1, our circuit will not settle at a particular output value (or voltage), meaning there is no well-defined propagation delay.

So now that we can build large combinational circuits, we're going to focus today on how to specify the function of such a device. As mentioned last time, we can use **truth tables** (which enumerate all output values for all possible input values).

#### Example 49

Suppose we have a combinational device which takes in three bits A, B, C. If C = 0, then the output Y is taken to be A, and otherwise it's taken to be B.

Then the truth table can be written out as follows: we try every possible combination (A, B, C) and mark down the value of Y. (Usually, they are written vertically instead of horizontally – the rotation is just to save space.)

| С | 0 | 0 | 0 | 0           | 1 | 1 | 1 | 1 |

|---|---|---|---|-------------|---|---|---|---|

| В | 0 | 0 | 1 | 1           | 0 | 0 | 1 | 1 |

| А | 0 | 1 | 0 | 0<br>1<br>1 | 0 | 1 | 0 | 1 |

| Y | 0 | 1 | 0 | 1           | 0 | 0 | 1 | 1 |

While this is a valid approach, and we can write down a truth table for any such function (with  $2^n$  possible inputs if we have *n* binary inputs), we're going to talk about a second form, **Boolean expressions**, today. Boolean expressions are equations that contain binary variables (0 or 1), as well as three operations AND (denoted  $\cdot$ ), OR, (denoted +), and NOT (denoted with an overbar). For example, the above function can also be written as

$$Y = \overline{C} \cdot A + C \cdot B.$$

It turns out that **all combinational functions can be specified with Boolean expressions**, and this is nice because writing out expressions takes less space, and manipulating them is relatively simple.

Before we discuss this more, we want to return to the question of **how fast circuits are**. We said before that we need a **propagation delay**, an upper bound on how long it takes to get from valid inputs to valid outputs. If we plot the output voltage of a device  $V_{out}$  as a function of the input voltage  $V_{in}$ , there will be some lag or transit time between the time when the input value becomes a valid input bit, and the time when the output value is a valid output bit. (Remember that this means we need to measure how long it takes for the voltage to switch from  $V_{OH}$  to  $V_{OL}$ , or vice versa.)

This propagation delay  $t_{PD}$  should be minimized when possible, and the reason for this is that many processors run at **certain clock frequencies**. For example, if the frequency  $f_{CLK}$  is about 4 GHz, then  $t_{CLK} = \frac{1}{f_{CLK}} = 250$  picoseconds is the time between **clock periods** of the processor. In other words, every  $t_{CLK}$ , our processor will change the inputs into our system and read the outputs. So we need an upper bound to ensure that we can run in the necessary time in the worst-case. The idea is that we have a kind of **combinational contract**, which tells us that there are no promises in some short amount of time after we change our inputs, but that we will have the correct, valid outputs after a while.

There's also another quantity we will soon care about:

#### Definition 50

The contamination delay  $t_{CD}$  is a lower bound on how long it takes to go from invalid inputs to invalid outputs.

This will be more important when we have state elements in sequential circuits – it's okay for us to ignore this  $t_{CD}$  for now.

So now we'll return to **Boolean algebra**, which is a way to describe and work with Boolean expressions.

# **Definition 51**

The AND, OR, and NOT operators are defined as follows:

- AND is a binary operator that outputs 1 if both input bits are 1, and 0 otherwise.

- OR is a binary operator that outputs 1 if either input bit is a 1, and 0 otherwise.

- NOT is a unary operator which outputs the opposite bit that is input.

**Remark 52.** We may also see "NOT a" written as  $\neg a$  or !a or  $\sim a$  rather than  $\overline{a}$ , and we may see different notation for AND and OR from logicians  $(\land, \lor)$  and programmers (& or &&, and | or ||).

It turns out that all Boolean algebra can be derived from AND, OR, and NOT, and we can specify that in a rigorous mathematical way. Specifically, we use the following set of axioms:

- **Identity**:  $a \cdot 1 = a$  and a + 0 = a for all a,

- Null:  $a \cdot 0 = 0$  and a + 1 = 1 for all a, where we remember that + is OR,

- Negation:  $\overline{0} = 1$  and  $\overline{1} = 0$ .

It turns out that there's a curious symmetry between the first and second axiom in each bullet point: if we switch ORs with ANDs, and we replace 0s with 1s, that gives us another true statement. This is called a **duality principle**, and because it holds for the axioms (which derive all other expressions), **this duality principle holds for all expressions**!

And either using truth tables or axioms, we can derive a few useful properties: **commutativity, associativity, and distributivity** appear much like they do in "normal" addition and multiplication, except that the distributivity laws now look like

$a \cdot (b+c) = a \cdot b + a \cdot c, \quad a+(b \cdot c) = (a+b) \cdot (a+c).$

(So OR and AND each distribute over each other!) We also have the following properties:

- **Complements**:  $a \cdot \overline{a} = 0$  and  $a + \overline{a} = 1$ ,

- Absorption:  $a \cdot (a + b) + a$  and  $a + a \cdot b = a$ ,

- **Reduction**:  $a \cdot b + a \cdot \overline{b} = a$  and  $(a + b) \cdot (a + \overline{b}) = a$ ,

# • **De Morgan's Law**: $\overline{a \cdot b} = \overline{a} + \overline{b}$ , and $\overline{a + b} = \overline{a} \cdot \overline{b}$ .

We should try to familiarize ourselves with these statements by proving them – this can be done either by working algebraically, from the axioms, or we can write out truth tables and verify that everything matches up.

**Remark 53.** Just like in ordinary arithmetic, multiplication (AND) precedes addition (OR) in the absence of parentheses.

#### Example 54

Suppose we want to show that  $a \cdot b + a \cdot \overline{b} = a$  for all bits *a*, *b*, using some of the other results.

Then the relevant calculation is that

$$a \cdot b + a \cdot \overline{b} = a \cdot (b + \overline{b}) = a \cdot 1 = a,$$

by using distributivity, complements, and identity respectively.

Now we're ready to think about the statement we made earlier, which is that **truth tables and Boolean expressions are equivalent**. Going from a Boolean expression to a truth table can be done by evaluating every possible value, but the converse is not as clear.

# Fact 55

Given a truth table, we can produce an equivalent Boolean expression by writing a **sum of product terms**, where each term covers a single 1 in the truth table.

For example, suppose we have Y as a function of the bits C, B, A, like in the above example. Then if Y = 1 at (C, B, A) = (0, 0, 1), then the expression

$\overline{C} \cdot \overline{B} \cdot A$

is a **product term** (which only consists of variables or their negations ANDed together) which takes on the value 1 at (0, 0, 1) and 0 otherwise. So if we want to write down an expression for Y, we can **repeat this process for all rows** where the product is 1, and that gives us an expression that looks like

$$Y = \overline{CB}A + \overline{C}BA + CB\overline{A} + CBA.$$

(The product is implicit here, just like in integer algebra.) This kind of expression is called the function's (disjunctive) **normal form**: it's unique, but it might not be the simplest or shortest expression for the function.

And now we can use Boolean expressions to think about building good circuits: the process of building logic circuits from expressions is called **logic synthesis**.

#### **Definition 56**

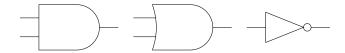

A **logic gate** is a combinational device that represents a simple function (such as AND, OR, or the inverter NOT). A **logic diagram** is a circuit representation of a Boolean expression with logic gates and wires.

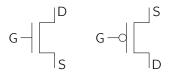

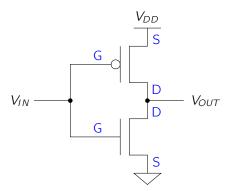

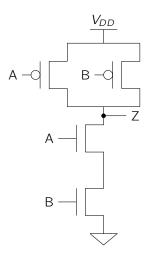

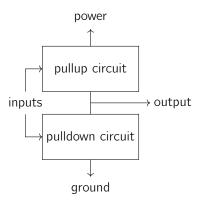

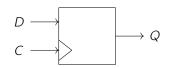

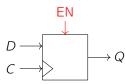

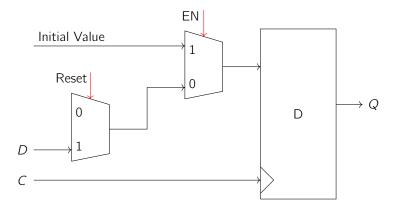

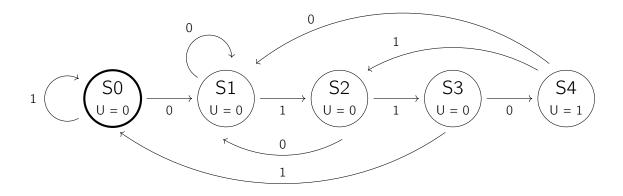

The AND, OR, and inverter (or NOT) gates are shown below, in order: